※ 해당 게시글은 주제를 탐구하면서 주관적인 생각을 정리 한 글입니다.

※ 해당 게시글은 https://www.youtube.com/@BranchEducation SSD 관련 영상을 참고하였습니다.

이전 글을 통해서

전자기학의 앙페르 법칙과 전자기 유도(페러데이 법칙),

그리고 강자성체의 자기화의 원리를 통해

데이터를 저장하는 장치들을 살펴보았다.

이를 바탕으로 자기 테이프, 자기, 드럼, 플로피 디스크, 하드 디스크 등

비휘발성 메모리의 원리를 이해할 수 있었다.

또한,

레이저를 이용한 저장 방식인 CD/CD-ROM에 대해서도 알아보았다.

[컴퓨터][32] 비휘발성 저장 장치 - 2 (자기 테이프, 플로피 디스크, 하드 디스크:HDD)

※ 해당 게시글은 주제를 탐구하면서 주관적인 생각을 정리 한 글입니다.이전 글을 통해 컴퓨터의 전원이 꺼져도디지털 정보를 저장하고 유지할 수 있는 비휘발성 메모리ex) CD, HDD, SSD 등

core-basic.tistory.com

그러나 현재 대부분의 사람들은 SSD를 사용한다.

SSD는 기존 저장 장치들과 달리 강자성체나 레이저를 이용하지 않는다.

대신, 전자기학과 양자역학의 원리를 바탕으로

전자의 양에 따라 데이터를 기록하는 방식을 사용한다.

이번 글에서는 SSD의 데이터 저장 원리를 자세히 탐구해 보겠다.

< 비휘발성 메모리 - 3 >

( Solid-State Drive , SSD )

해당 게시글은 다음 영상을 참고하였습니다.

< SSD 구조 >

SSD에서 실질적으로 데이터를 저장하는 공간은

전하 트랩 플래시 메모리 셀

(Charge Trap Flash Memory Cell, CTF 메모리 셀)이다.

이에 따라 메모리 셀을 시작으로

SSD의 전체적인 구조를 탐구해 보겠다.

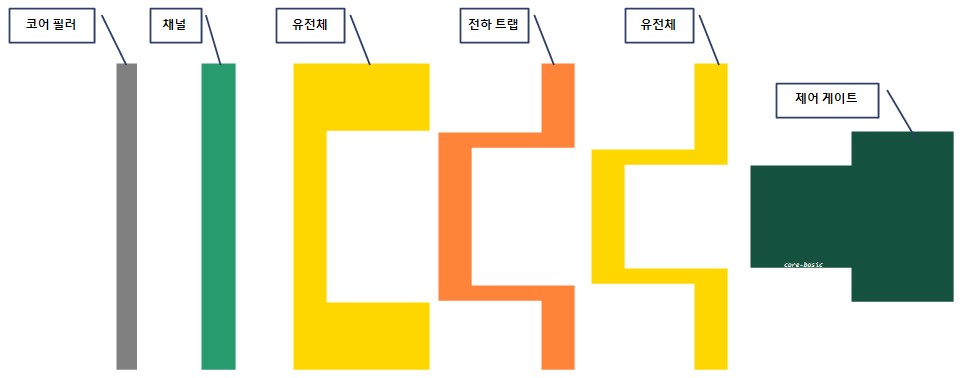

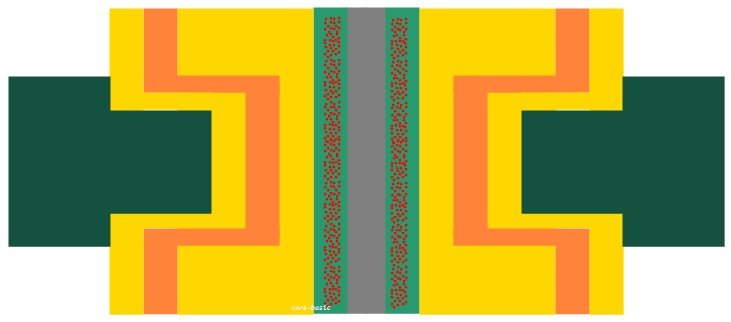

" 전하 트랩 플래시 메모리 셀(Charge Trap Flash Memory Cell) ”

전하 트랩 플래시 메모리 셀(Charge Trap Flash Memory Cell)은

SSD에서 정보를 저장하는 최소 단위이자 기본 구조를 이루는 요소이다.

메모리 셀은 원기둥 형태의 코어필러와 채널을 중심으로 바깥쪽을

유전체, 전하트랩, 다시 유전체 그리고 제어 게이트가

겹겹이 감싸는 구조로 되어 있다.

※ 코어 필러 :

- 고유전율(High-K) 유전체 구성되어 있다.

- 마카로니(속이 빈 원기둥) 형태를 유지하여 전하 트랩과 게이트의 영향을 잘 전달하고,

채널을 효과적으로 제어하는 역할을 한다.

※ 채널 :

- N형으로 도핑되어 있거나, 도핑되지 않은 폴리실리콘으로 구성되어 있다.

- 기본적으로 전자가 흐르는 경로를 제공한다.

(일반적으로 전자는 흐르지 않으며, 전압을 가해야 전자가 잘 흐른다.)

※ 유전체 :

- 이산화 규소(SiO2)로 구성되어 있다.

- 채널과 전하 트랩 사이, 그리고 전하 트랩과 게이트 사이에 위치하여

전자가 넘나드는 것을 것을 막는(저항하는) 역할을 한다.

※ 전하 트랩 :

- 폴리실리콘 질화물(질화규소:Si3N4)로 구성되어 있다.

- 전도성이 없는 유전체 성질을 가지면서 전자를 저장하는 기능을 한다.

※ 제어 게이트 :

- 금속(TiN, W, TaN 등)과 고유전율 절연체(High-K)로 구성된다.

- 전압을 가하면 채널에 전류가 흐르며,

이를 통해 전하 트랩에 전자가 주입되거나 제거되어 데이터를 기록한다.

※ 움푹 들어간 구조 :

- 전하가 인접한 셀로 누설되는 것을 방지하여 데이터 간섭을 줄이는 역할을 한다.

※ 해당 기술은 트랜지스터 MOSFET 계열 중 하나인 플로팅 게이트 트랜지스터에서 파생되었다.

" 스트링(String) 구조 "

전하 트랩 플래시 메모리 셀 (Charge Trap Flash Memory Cell)

에 대해서

메모리 셀 (예시로) 10개를 서로 위아래로 겹쳐져 있는 구조를

스트링(String) 구조 라고 한다.

※ 스트링 구조는 TB기준 약 96~136개 정도의 메모리 셀로 구성된다.

스트링 구조에서 정보를 저장하거나 읽을 때는

한 번의 하나의 셀만 활성화될 수 있다.

이를 위해서 각 층, 메모리 셀마다 별도의 제어 게이트가 배치된다.

그리고, 최상단 층 위에는 bitline이 배치되어 있어,

제어 게이트의 동작에 따라 채널을 통해 흐르는 전자 또는

전기 신호를 다른 칩이나 장치로 전달할 수 있다.

※ 추가적으로 최상단 층과 최하단 층에 추가적인 제어 게이트를 배치한다.

※ 추가된 최상단 제어 게이트는 Bitline 선택기이다. 따라서 최상단 제어 게이트에 전압을 가하면, 아래에서 전달된 값이 Bitline을 통해 외부로 출력될 수 있다.

※ 추가된 최하단 제어 게이트는 소스 라인 선택기라고도 하며, 정보 블록을 지우는 것과 관련이 많다.

" 행(Row) 및 페이지(Page) "

나아가 더 많은 정보를 저장하기 위해

스트링(String) 구조를 여러 개 복제하여

가로로 나열하였을 때 생성되는 2차원 면을 행(Row)라고 한다.

그리고

행(Row)에서 하나의 층, 가로 줄을 페이지(Page)라고 부른다.

예를 들어,

스트링(String) 구조를 32번 복제하여 하나의 행을 구성하면,

다음과 같이 bitline도 스트링 수에 맞추어 32개가 추가로 배치된다.

추가적으로, 같은 페이지(Page)에 속하는 모든 메모리 셀들은

제어 게이트를 공유하여,

32개의 인접한 메모리 셀로 구성된 페이지 전체가

동시에 활성화 및 비활성화된다.

※ TB기준, 하나의 행(Row)에는 약 500~1200개의 페이지(Page)로 구성된다.

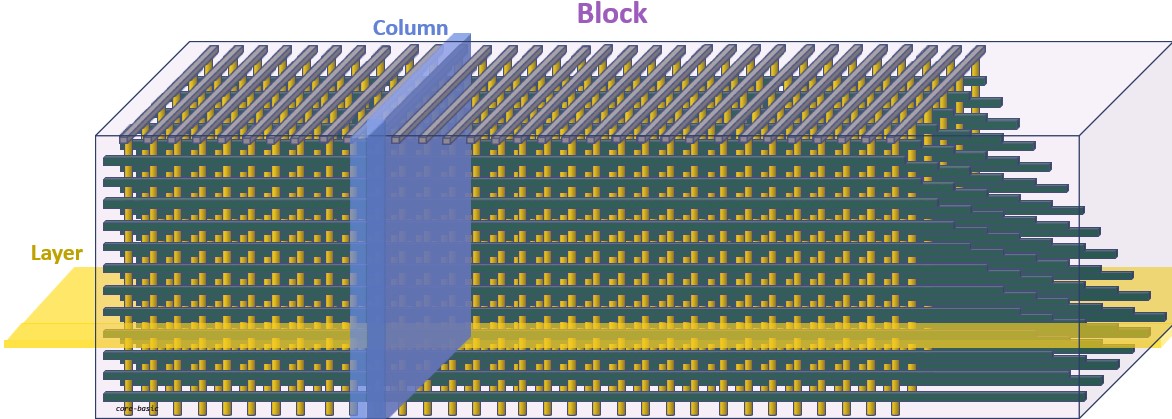

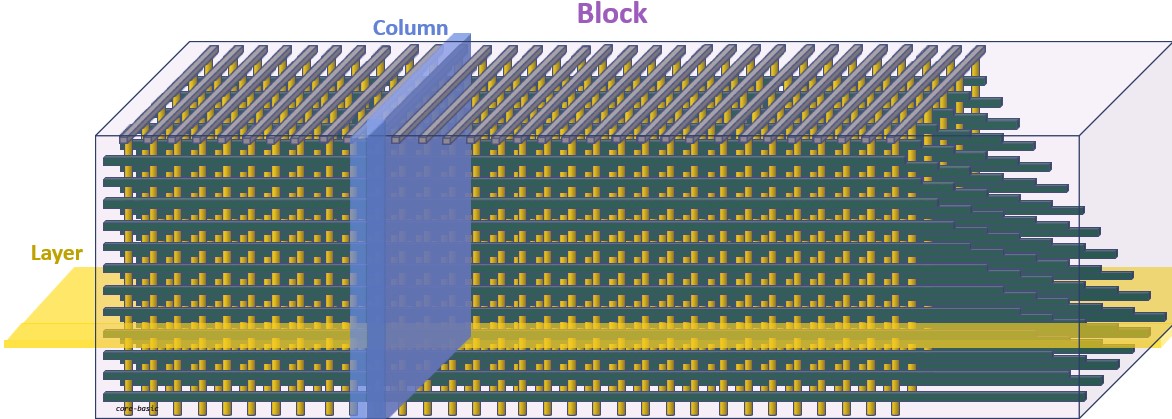

" 블록(Block) 및 열(Column) 그리고 층(layer) "

더욱더 많은 정보를 저장하기 위해 행(Row) 구조를 복사하여

깊이 배치하였을 때 생성되는 3차원 구조를 블록(Block)이라 한다.

그리고

블록(Block)에서 하나의 세로 단면(2차원) 구조를 열(Column)이라고 부르고,

하나의 수평 단면(2차원) 구조를 층(Layer)이라고 부른다.

이에 따라 예시로

만약 행(Row) 구조를 6번 복제하여 블록(Block)을 구성하면,

같은 열(Column)에 있는 메모리 셀들은 같은 bitline을 공유하고,

같은 층(layer)에 있는 메모리 셀들은 제어 게이트를 공유한다.

그리고 Block에서의 bitline은

bitline selectors(최상층 제어 게이트)를 통해

선택된 열에 있는 스트링 중 하나의 스트링만

bitline을 통해 데이터를 송수신할 수 있다.

또, 행(Row) 구조를 6번 복제하여 block을 형성하는 경우

한 층(Layer)에는 6개의 페이지(Page)가 존재하며

Contorl Gate Selectors(제어 게이트 선택기)에 의해

6개의 페이지가 모두 활성화 또는 비활성화된다.

이를 통해서

SSD는 한 번에 하나의 열(Column)과 층(Layer)을 선택하여

단일 페이지(Page) 단위로, 정보를 저장하거나 읽을 수 있다.

※ 블록(Block)은 TB기준 행(Row)의 4~8줄로 구성된다.

※ 하지만 컴퓨터가 정보를 지울 때는 블록 단위로 지운다.

※ 지우기 과정에는 약 25V~30V에 해당되는 높은 전압이 필요한데 이는 내부 구조를 파괴시킬 수 있기 때문에 횟수를 줄인다.

※ 만약 특정 페이지만 지우고 싶을 때는 이외 다른 페이지들을 다른 블록으로 이동시킨 후, 전체 블록을 삭제한다.

※ bitline selectors + Contorl Gate Selectors = Row decoder

" 3D-NAND / V-NAND(Vertical NAND) "

전하 트랩 플래시 메모리 셀 : charge Trap Flash Memory Cell을

수직(Vetical)으로 열결 한 스트링 구조가

3D-NAND(V-NAND) 기술의 핵심이다.

이를 기반으로 Row, Block 등의 구조 또한

3D-NAND/V-NAND 기술 및 구조가 적용되었다고 볼 수 있다.

" Planes "

8TB 기준 3000~8000개의 블록(Block)이

하나의 Plane(평면)을 구성한다.

※ Page buffer는 수많은 블록들의 bitline과 이어져 있으며 데이터를 외부로 전달하거나 받기 위한 통로이다.

※ bitline selectors + Contorl Gate Selectors = Row decoder

" Die/Chiplet "

두 개의 Plane이 모여

하나의 Die(다이) 또는 Chiplet(칩렛)을 형성한다.

※ peripheral circuitry : 칩을 지원하기 위한 추가 회로

" NAND Flash Microchip "

약 1TB 기준 8개의 Die(Chiplet)와

8개의 서로 다른 Die(Chiplet)을 조정하기 위해서

인터페이스 칩을 추가하면

SSD에서 사용하는 하나의 마이크로칩(microchip)이 형성된다.

※ 현재는 16개 이상의 Chiplet은 쌓을 정도로 기술이 발전하였다.

※ SSD의 용량에 따라 마이크로칩은 여러 개 들어갈 수 있다.

※ 8TB = 약 18개의 낸드 플래시 마이크로칩이 포함된다.

" SSD 컨트롤러 마이크로칩"

SSD를 구성하는 여러 개의

NAND Flash Microcip과, DRAM이 연결되어

각 칩들 사이에서 인터페이스 및 통신을 담당한다.

또한, SSD와 연결된 컴퓨터/서버와도 인터페이스 및 통신한다.

※ SSD에 1개만 배치되어 있다.

※ 각 NAND Flash Microcip과 연결된 선을 Memory Channel(메모리 채널)이라 부른다.

※ Memory Channel을 통해서 NAND Flash Microcip에 데이터를 쓰거나 읽는 명령어를 보낸다.

※ 이외에도 Wear Leveling, Garbage Collection, Error-Correction Code 등의 기능을 수행한다.

" DRAM Chip "

SSD에는 TB기준 약 8개의 DRAM이

컨트롤러 마이크로칩과 연결되어 있다.

DRAM은 Translation Table(조회 테이블/변환 테이블)을 저장하고 있다.

Translation Table(조회 테이블/변환 테이블)은

NAND Flash Microcip에 저장되어 있는

데이터 정보들의 섹터 위치(가상 주소)를

Microchip 번호 : Die 번호 : Plane 번호 : Block 번호, Page 번호

(실제 주소)에 대응시켜 준다.

ex) Sector:10612315124 | 04:3:2:3950:453

이를 통해 컴퓨터는 섹터 주소(논리적 주소/가상 주소)만 알고 있어도,

SSD의 정확한 실제 주소(물리적 주소)를 찾아갈 수 있다.

※ SSD에서 Sector는 SSD의 저장 단위인 메모리셀에 대한 논리적/가상 주소이다.

※ 이에 따라 메모리 셀이 약 100억 개 있다면, 논리적 주소는 약 100억 개가 생성된다.

※ 테이블은 지속적으로 업데이트된다.

< SSD 정보 저장 방법 >

전하 트랩 플래시 메모리 셀에서는

전하 트랩에 저장된 전자의 양을 조절하여 정보를 저장할 수 있다.

" 1bit 전하 트랩 플래시 메모리 셀 정보 저장 "

(단일 레벨 셀 : SLC)

초기에는 전자량에 따른 두 가지의 상태만 구별이 가능했다.

즉, 전자가 매우 많은 상태(1) 또는 전자가 매우 적은 상태(0)로

단일 비트 정보를 저장하는 방식이었다.

" 3bit 전하 트랩 플래시 메모리 셀 정보 저장 "

(3중 레벨 셀 : TLC)

이후 과학자들은 더 다양한 전하량을 포획(trap)하고

측정할 수 있도록 정밀하게 조정할 수 있는 기능을 개발했다.

이에 따라 2020년대에 들어서 대부분 메모리 셀이

8개의 서로 다른 전하 레벨을 가질 수 있었으며,

이를 통해 하나의 메모리 셀에 3bit를

저장할 수 있게 되었다.

전자가 매우 많은 상태 = 000 = 0

001 = 1

010 = 2

011 = 3

100 = 4

101 = 5

110 = 6

전자가 매우 적은 상태 = 111 = 7

위와 같이 전하 트랩에 충전된 전자는

수십 년 동안 안정적으로 유지될 수 있다.

이를 통해 SSD(Solid state drive)에 데이터를 저장할 수 있다.

※ 더 나아가 최신기술은 16개의 다른 전하 레벨을 구별할 수 있도록 발전했으며, 이를 통해 4bit 저장이 가능한 QLC(Quad Level cell) 메모리가 개발되었다.

" 전하 트랩 플래시 메모리 셀 정보 저장 원리 "

그렇다면 전하 트랩 플래시 메모리 셀은 어떻게 데이터를 저장할까?

어떻게 채널에 있는 전자들을 전하 트랩으로 이동시킬 수 있었을까?

이에 대한 자세한 원리를 파악하기 위해서는

양자역학 관점에서 바라보아야 한다.

앞서 언급하였듯 과학자들은 전자를 전하 트랩에 가두어(Trap)

전자의 양에 따라 0과 1 뿐만 아니라,

0~7까지의 값과 대응시켜 데이터를 저장했다.

이에 따라 전자를 전하 트랙에 가두기 위해서

전하 트랙을

비전도성 절연체(이산화 규소:SiO2)로 구성된 유전체로 둘러싸았다.

그래서 전하 트랩에 있는 전자들은

유전체의 높은 에너지 장벽(밴드 갭) 때문에

전자는 수년 동안 안정적으로 전하 트랩 내부에 유지될 수 있다.

하지만, 전자가 생성되고 흐르는 곳은 채널인데,

전하 트랩을 유전체로 둘러싸면은

어떻게 전자가 채널에서 유전체를 건너

전하 트랩으로 이동시킬 수 있는지 의문점이 생긴다.

즉, 어떻게 메모리셀에 정보를 저장할 수 있을까?

이러한 문제를 해결하기 위해 전자기학과 양자역학 기술이 사용된다.

고전역학에 따르면 전자는 에너지 준위를 갖는 점전하로,

유전체를 통과하려면 매우 높은 에너지가 필요하다.

그런데 전자에 높은 에너지를 가할 수 있지만,

그로 인해 유전체의 구조가 붕괴될 수 있다.

하지만 양자역학적 관점에서는 전자의 위치는 점이 아닌,

발견될 가능성이 높은 곳을 나타내는 확률 밀도 또는 구름을 가진다.

이에 따라 만약 전하 트랩과 채널사이의 유전체가

적당한 간격으로 배치되어 있고,

제어 게이트에 적당한 양의 전압(16.5~22.5V)을 인가한다면,

전자기 원리에 의해 전압의 크기에 따라

채널에 존재하는 음전하 전자를 끌어당겨

전하의 확률 밀도/구름 또한 전하 트랩 쪽으로 끌어당길 수 있다.

※ 전하 트랩과 채널의 사이의 유전체의 간격은 원자 75~100개 크기에 불과하다.

※ 과학자들은 양자역학 방정식을 이용해 유전체 적당한 간격과 게이트 전압을 알아내었다.

※ 만약 유전체의 간격이 너무 좁으면 전압을 가하지 않아도, 넘어갈 수도 있다.

※ 16.5V ~ 22.5V 승압 전압을 적용해 전압이 올라가는 각 단계에서 특정 전하 트랩의 임계 전압을 측정한다.

※ 원하는 임계전압에 도달하면 게이트에 인가되는 전압 증가가 중단된다.

이를 통해 전자가 유전체를 넘어

전하 트랩에 위치할 확률이 상당히 높아진다.

이는 마치 유전체에 터널이 생겨 전자가 넘나드는 것과 같아

이와 같은 현상을 “양자 터널링”이라 부른다.

따라서 전하 트랩 플래시 메모리 셀은 “양자 터널링” 원리를 이용하여

정보를 저장할 수 있다.

※ 전자가 전하트랩(SiN)에 위치하면 폴리실리콘 경계층 사이에 갇힌다.

※ SiO2(유전체)의 에너지 밴드 갭은 8.9eV이다. 유전강도 즉, 파괴 전압은 1E7 [10^7] V/cm이다.

" 3bit 전하 트랩 플래시 메모리 셀 저장 원리 "

앞서 양자 터널링 원리를 통해 채널에 존재하는 전자를

전하 트랩에 포획(trap)할 수 있다는 것을 알 수 있었다.

그렇다면

하나의 메모리 셀 안에 0~7까지의 값을 저장하는 원리는 무엇일까

만약 제어 게이트 16.5V ~ 22.5V까지

점진적으로 상승하는 전압을 가할 경우

전하 트랩에는 점차 더 많은 전자가 포획된다.

이를 활용해 과학자들은 전압에 따른 전자의 양을 8개의 레벨로 나누었다.

전자가 매우 많은 상태를 = 000, 전자가 매우 적은 상태 = 111로

설정하여 하나의 메모리 셀에 3BIT를 저장할 수 있게 되었다.

※ 제조사에 따라 이진 값의 대응 방식은 다를 수 있다.

이러한 8개 레벨을 정확히 구분하려면,

채널에서 전류가 흐르게 하는 최소한의 접안인

임계 전압(threshold voltage)을 이용해야 한다.

제어 게이트는 채널에 있는 전자의 흐름을 조절하는 역할을 한다.

기본적으로 채널에 전자는 존재하지만 흐르지는 않으며,

이 상태를 OFF(꺼짐) 상태라고 한다.

게이트에 전압을 가하면 전기장이 형성되면서

전자가 흐를 수 있는 상태, 즉 ON(켜짐) 상태가 된다.

이때 채널을 ON상태로 활성화는 데 필요한 최소 전압을

임계 전압이라고 한다.

※ 일반적으로 게이트에 0V만 인가되어도 채널이 켜지고, 음전압을 인가해야 채널이 꺼진다.

그러나 전하 트랩에 전자가 많을수록

전기장을 방해하여, 임계 전압이 증가한다.

즉, 전하 트랩에 저장된 전자량에 따라

게이트에 더 높은 전압을 가해야 채널이 활성화된다.

그래서 게이트의 전압이 채널을 활성화하는데

필요한 임계 전압보다 낮으면,

채널이 꺼지게 되고, 전자는 채널을 통해 흐를 수 없다.

그리고

게이트 전압이 임계값보단 높으면

채널이 켜지고 전자가 흐를 수 있다.

그런데 만약 게이트에 전압을 인가하여

전하 트랩에 전자들이 존재할 경우

해당 전자들은 전자기 원리에 따라

게이트 전압에서 방출되는 전기장을 방해하고,

채널이 켜지는 것을 방해한다.

이에 따라

전하 트랩에 있는 전자에 의해 발생하는 방해 전기장을 제압하기 위해서는

게이트에 더 강한 전압이 필요하게 된다.

과학자들은 이러한 원리를 활용하여

게이트에 (저장) 전압을 ex) 18V부터 가하면서,

전하 트랩에 특정한 양의 전자를 저장하여

채널의 임계 전압을 변환시켰다.

이후, 게이트 (읽기) 전압을 0V부터 점진적으로 인가하며,

채널이 활성화되는 전압을 측정하여 8개의 임계전압을 결정한다.

이를 바탕으로 각 임계 전압에 대응되는 (저장) 전압을 분석하여

(저장) 전압 또한 8개의 범위로 구분할 수 있다.

결과적으로 각 메모리셀의 제어 게이트에 특정 (저장) 전압을 가해

3BIT를 저장할 수 있게 되었다.

※ 읽기 전압은 약 0 ~ 4.5V, 저장 전압은 약 16.5 ~ 22.5V에 해당된다.

"스트링 구조에서의 정보 저장 방법 "

그리고 앞서 언급하였듯이

만약 메모리 셀 10개를 서로 위에 겹쳐져 있는

스트링(String) 구조가 있을 때 정보를 저장하거나 읽고자 한다면,

한 번의 하나의 셀만 활성화시켜 정보를 저장할 수 있다.

이에 따라 우선

스트링 구조 최상위에 존재하는 bitline을 활성화하고,

각 층/ 각 셀마다 배치되어 있는 별도의 제어 게이트를 이용하여

스트링 구조의 가장 아래층부터

제어 게이트에 약 16.5V ~ 22.5V 사이의 양 전압을 부여하여

전압의 크기에 따라 전하 트랩에 저장할 전자의 양을 결정한다.

1bit 메모리 셀의 경우

0(전자의 양 많음) 또는 1(전자의 양 적음)을 저장할 수 있고,

3bit 메모리셀의 경우

0(전자의 양 많음) ~ 7(전자의 양 적음) 값 중

하나를 저장할 수 있다.

자세한 저장 원리는 앞서 언급한 메모리셀의 저장 원리와 같이

양자역학 터널링 원리와 임계전압의 활용을 따른다.

위의 과정에서 핵심은 한 층에서만 쓰기가 이루어진다는 점이다.

" 행(row) 및 페이지(Page) 구조에서의 정보 저장 과정 "

나아가 더 많은 정보를 저장하기 위해 스트링 구조를 복사하여,

다음과 같이 가로로 나열하여 2차원 행(Row) 구조를 형성하였을 때,

하나의 층, 가로줄은 페이지(Page)라고 부른다.

이에 따라 만약 예시로

스트링(String) 구조를 32번 복제하여 행을 구성하면

각 스트링의 최상층에는 bitline과 bitline selectors가 배치되고,

각 페이지는 공통 제어 게이트를 공유하여,

32개의 인접한 메모리 셀로 구성된 페이지 전체가

동시에 활성화 및 비활성화된다.

이에 따라,

SSD는 단일 페이지(Page) 단위로 정보를 저장하거나 읽을 수 있다.

" 블록(Block) 및 행(Row) x열(Column) 구조에서의 정보 저장 과정 "

한 번 더 나아가 더욱 많은 정보를 저장하기 위해

행(Row) 구조를 복사하여

깊이 나열하였을 때 생성되는 3차원 구조를 블록(Block)이라 한다.

그리고

블록(Block)에서 하나의 세로 면(2차원) 구조를 열(Column)

이라고 부르고,

하나의 밑면(2차원) 구조를 층(Layer)이라고 부른다.

이에 따라 예시로 만약 행(Row) 구조를 6번 복제하여

블록(Block)을 구성하면,

같은 열(Column)에 있는 메모리 셀들은 같은 bitline을 공유하고,

같은 층(layer)에 있는 메모리 셀들은 같은 공통 제어 게이트를 공유한다.

※ 블록(Block)은 TB기준 행(Row)의 4~8줄로 구성된다.

※ Block에서의 bitline은 bitline 선택기를 통해 같은 열에 있는 스트링 구조 중 하나의 스트링에서만 데이터를 송수신한다.

※ 행(Row) 구조를 6번 복제하여 block을 형성하는 경우 한 층(Layer)에는 6개의 페이지(Page)가 존재하며 공통 제어 게이트에 의해 6개의 페이지가 모두 활성화 또는 비활성화된다.

※ 하지만 컴퓨터가 정보를 지울 때는 블록 단위로 지운다. 지우기 과정에는 약 25V~30V가 필요하기 때문이다.

※ 만약 특정 페이지만 지우고 싶을 때는 이외 다른 페이지들을 다른 블록으로 이동시킨다.

" Block 및 행(Row) x열(Colimn) 구조에서 단일 메모리 셀 저장 방법 "

앞선 내용에 따르면 SSD는 단일 페이지(Page) 단위로,

정보를 저장하거나 읽을 수 있다.

하지만

만약 하나의 메모리 셀에만 접근하고 싶다면 어떻게 해야 할까?

이를 "특정 전하 트랩만 쓰이지 않도록 하는 방법"으로

바라볼 수도 있다.

그래서 전하 트랩에 전자가 저장되지 않도록 하려면,

해당 메모리 셀의 채널에 8V의 바이어스 전압을 인가하면 된다.

예를 들어 메모리 셀에 저장하기 위해서

최소 18V의 전압차가 필요한데 채널에 8V가 인가되어있으면,

실질적으로는 12V의 전압차 이므로,

이는 전자가 터널링 하기에 충분히 강하지 않게 된다.

이후 게이트 전압이 0V로 떨어지고,

각 채널이 켜져 있는지, 꺼져있는지 확인하여,

전자가 예상대로 해당 전하 트랩으로 이동했는지 확인한다.

만약 채널이 켜져 있으면

전자가 전하 트랩에 저장되지 않은 것이고,

채널이 꺼져 있으면

전자가 전하 트랩에 저장된 것이다.

나아가 더 큰 값 즉,

더 많은 양의 전자를 저장하기 위해서 18.3V로 설정하고,

다시 변경을 원하지 않는 메모리셀들은 채널을 8V로 바이어스 한다.

이러한 과정을 통해

각 메모리셀이 원하는 수의 전하를 전하트랩에 넣을 때까지 반복한다.

※ 단일 셀에서 전자가 없을 때 임계 전압은 -0.5V이다. 전자가 있을 때는 임계 전압은 약 3V이다. 그리고 채널에서 전하 트랩으로 전자 밀도/구름을 끌어오는데 게이트에는 약 16.5~22.5V가 필요하다.

※ TLC:3bit 메모리셀에서는 쓰기 전압은 유지되지만, 임계전압은 0~4.5V로 나뉜다.

< SSD 정보 읽기 방법 >

SSD에서 데이터를 저장하는 기본 단위 또한,

전하 트랩 플래시 메모리 셀

(Charge Trap Flash Memory Cell, CTF 메모리 셀)이다.

따라서 데이터를 읽는 과정 역시 메모리 셀에서 수행된다.

메모리 셀에서 데이터를 읽는 원리는

데이터를 저장하는 과정과 유사하지만,

가장 큰 차이점은 요구되는 전압의 크기이다.

※ 읽기 전압 : 0 ~ 4.5V , 쓰기 전압 : 16.5 ~ 22.5V

※ 전하 트랩에 저장된 전자 전하레벨을 측정할 때는 전하 트랩의 전하량은 변하지 않는다.

" 전하 트랩 플래시 메모리 셀 정보 읽기 원리 "

앞선 내용에서 설명하였듯이

전하 트랩 플래시 메모리셀에서 제어 게이트는

채널에 있는 전자의 흐름을 조절하는 역할을 한다.

기본적으로 채널에 전자는 존재하지만, 흐르지는 않으며,

이 상태를 OFF(꺼짐) 상태라고 한다.

게이트에 전압을 인가하면 전기장이 형성되어

전자가 흐를 수 있는 ON(켜짐) 상태가 된다.

이때 채널을 ON상태로 활성화는 데 필요한 전압을

임계 전압이라고 한다.

(저장 과정 내용과 같다.)

※일반적으로 게이트에 0V만 인가되어도 채널이 켜지고, 음전압을 인가해야 채널이 꺼진다.

하지만 만약 메모리 셀에 정보가 저장되어 있는 경우

전하 트랩에 전자가 채워져 있으므로, 게이트에 전압을 인가하면

전하 트랩에 저장된 전자들이

게이트 전압에서 형성되는 전기장을 방해하여,

채널이 켜지지 않는다.

따라서 전자가 저장된 메모리 셀의 경우, 임계 전압이 높아져

채널을 활성화하는데 더 높은 전압이 필요하게 된다.

이러한 원리를 이용하면,

저장된 전하량에 따라 서로 다른 임계 전압 차이가 발생하고

이를 통해 메모리 셀의 상태를 읽을 수 있다.

예시를 들어 쉽게 설명해 보자면

만약 저장된 전자가 없는 메모리 셀과,

저장된 전자 있는 메모리 셀이 있을 때

두 메모리 셀에 작은 전압을 인가하면,

저장된 전자가 없는 메모리셀의 채널이 켜져 전자가 흐를 것이고,

저장된 전자가 있는 메모리셀은 임계 전압값이 커져

채널에 전자가 흐르지 않을 것이다.

그리고 다시 더 높은 전압을 인가하면

저장된 전자가 있는 메모리셀의 채널도 켜져 전자가 흐르게 된다.

※ 단일 셀에서 전자가 없을 때 임계 전압은 -0.5V이다.

※ 1BIT 메모리 셀에서 전자가 있을 때는 임계 전압은 약 3V이다.

※ 3BIT 메로리 셀에서의 임계전압은 0 ~ 4.5V로 나뉜다.

이에 따라 두 메모리셀이 서로 다른 전압에서 채널이 켜지므로

채널 활성화 여부를 통해서 두 메모리셀의 임계전압이 다르고,

따라서 전하 트랩에 저장된 전자의 수도 다르다는 것을 알 수 있다.

만약 채널이 작은 전압에서 켜지면,

전하 트랩에 적은 전자가 있다는 것을 뜻하며,

이 낮은 수준의 저장된 전하를 이진수 1로 지정할 수 있다.

채널이 더 높은 전압에서 켜지면,

전하 트랩에 많은 전자가 있다는 것을 뜻하며,

이 높은 수준의 저장된 전하를 이진수 0으로 지정할 수 있다.

이러한 원리를 통해 더 나아가 각 메모리셀 마다 3BIT를 저장할 수 있는

트리플레벨셀(Triple Level Cell : TLC)을 구현할 수 있다.

8개의 다른 상태, 즉 3BIT 정보를 저장하기 위해서는

8개의 서로 다른 전자 레벨을 전하 트랩에 배치해야 한다.

그 결과 8개의 서로 다른 임계 전압이 생긴다.

그리고 각 전하 레벨은 게이트에 적용되는 전압의 크기에 따라 결정되며,

이는 채널이 켜지는 전압과 연관된다.

" 스트링 구조에서의 정보 읽는 방법 "

그리고 앞서 언급하였듯이

만약 메모리 셀 10개를 서로 위에 겹쳐져 있는

스트링(String) 구조가 있을 때 정보를 저장하거나 읽고자 한다면,

한 번의 하나의 셀만 활성화시켜 정보를 읽을 수 있다.

이때 이각 층/ 각 셀마다 배치되어 있는 별도의 제어 게이트를 이용하여

스트링 구조의 가장 아래층부터 제어 게이트에

적당한 크기의 양 전압을 부여하여,

해당 층의 전하 레벨을 측정하고,

해당 정보를 스트링 구조의 중심을 거쳐서

가장 최상단의 전선(bitline)으로 전송한다.

※측정 원리는 위의 메모리셀 데이터 읽기 원리에 따른다.

그리고 다음 층의 제어 게이트에 양 전압을 부여하여

전하 레벨을 측정하고 비트라인으로 전송한다.

이처럼 스트링 구조를 따라 아래층부터 위로 올라가며

각 셀의 전하트랩이 저장하고 있는 전자/전하량을 측정하여 bitline으로 전송한다.

※ 읽기에 필요한 전압은 0 ~ 4.5V 사이이다.

" 행(row) 및 페이지(Page) 구조에서의 정보 읽는 방법 "

나아가 더 많은 정보를 저장하기 위해 스트링 구조를 복사하여,

다음과 같이 가로로 나열하여 2차원 행(Row) 구조를 형성하였을 때,

하나의 층, 가로줄은 페이지(Page)라고 부른다.

이에 따라 만약 예시로

스트링(String) 구조를 32번 복제하여 행을 구성하면

각 스트링의 최상층에는 bitline과 Selector bitlines 배치되고,

각 페이지는 공통 제어 게이트를 공유하여,

32개의 인접한 메모리 셀로 구성된

페이지 전체가 동시에 활성화 및 비활성화된다.

이에 따라,

SSD는 단일 페이지(Page) 단위로 정보를 저장하거나 읽을 수 있다.

※ 측정 원리는 위의 메모리셀 데이터 읽기 원리에 따른다.

※ 읽기에 필요한 전압은 0 ~ 4.5V 사이이다.

" 블록(Block) 및 행(Row) x열(Column) 구조에서의 정보 읽는 과정 "

한 번 더 나아가 더욱 많은 정보를 저장하기 위해

행(Row) 구조를 복사하여 깊이 나열하였을 때

생성되는 3차원 구조를 블록(Block)이라 한다.

그리고 블록(Block)에서

하나의 세로 면(2차원) 구조를 열(Column)이라고 부르고,

하나의 밑면(2차원) 구조를 층(Layer)이라고 부른다.

이에 따라 예시로

만약 행(Row) 구조를 6번 복제하여 블록(Block)을 구성하면,

같은 열(Column)에 있는 메모리 셀들은 같은 bitline을 공유하고,

같은 층(layer)에 있는 메모리 셀들은

같은 공통 제어 게이트를 공유한다.

이를 통해서

SSD는 한 번에 하나의 열(Column)과 층(Layer)을 선택하여

단일 페이지(Page) 단위로, 정보를 저장하거나 읽을 수 있다.

※ 측정 원리는 위의 메모리셀 데이터 읽기 원리에 따른다.

※ 블록(Block)은 TB기준 행(Row)의 4~8줄로 구성된다.

※ Block에서의 bitline은 bitline 선택기를 통해 같은 열에 있는 스트링 구조 중 하나의 스트링에서만 데이터를 송수신한다.

※ 행(Row) 구조를 6번 복제하여 block을 형성하는 경우 한 층(Layer)에는 6개의 페이지(Page)가 존재하며 공통 제어 게이트에 의해 6개의 페이지가 모두 활성화 또는 비활성화된다.

※ 읽기에 필요한 전압은 0 ~ 4.5V 사이이다.

< SSD 정보 제거 방법 >

SSD 정보를 제거할 때는

게이트에 음전압을 인가하고, 채널에는 양전압을 인가한다.

이를 통해 정보를 저장하는 터널링 원리의 역방향으로

전하 트랩에 있는 전자 및 전자구름/확률을

다시 채널 방향 쪽으로 이동시켜, 전하 트랩에 전자를 제거한다.

이때 전압의 크기는 25~30V 전압에 해당되는

높은 전압이 필요하다.

이는 유전체를 손상시킬 수 있는 크기의 전압으로

SSD의 수명이 제한될 수 있다.

때문에 Block 단위로 기록을 제거하여 SSD의 손상을 최소화한다.

만약 특정 페이지만 지우고 싶을 때는

이외 다른 페이지들을 다른 블록으로 이동시킨다.

< 컴퓨터와 SSD의 통신 과정 >

" 컴퓨터/서버와 연결된 SSD로부터 데이터를 읽는 과정 "

(1)

SSD로부터 사진을 요청한다.

ex) Read, Sector:11357700897

(2)

SSD Controller는 요청한 주소 값에 대해 DRAM의 테이블을 조회하여

Chip:Die:Plane:Blcok:Page 값을 얻어온다.

ex) 10612315124 | 04:3:2:3950:453

(3)

SSD Controller는 NAND Flash Chip에 칩의 내용을 읽도록

Memory Channel을 통해 요청을 보낸다.

ex) Read, Address, 04(Chip):3(Die):2(Plane):3950(Block):453(Page)

(4)

NAND Flash Chip은 해당 주소에 접근하여

정보를 읽어 다시 Memory Channel을 통해 SSD Controller로 보낸다.

(5)

SSD Controller는 해당 정보를 다시 연결된 컴퓨터/서버로 라우팅/전송한다.

" 컴퓨터/서버왕 연결된 SSD로부터 데이터를 저장하는 과정 "

(1)

SSD에 사진을 사용하지 않은 섹터(논리적 주소)에

저장하라는 명령어를 보낸다.

ex) Save, Sector:11357700897, 01010100101…

(2)

SSD Controller는 해당 명령어를 받아 Sector(논리적 주소)에

정확한 실제 물리적 주소를(Chip:Die:Plane:Block:Page) 대응시켜

DRAM Translation Table에 기록한다.

(3)

이후 SSD Controller는 실제 주소를 기반으로

특정 페이지에 작성하라는 명령어로 변환하여

Memory Channel을 통해 NAND Flash Chip에 전송한다.

ex) Write, Address, 04:3:2:3950:453, 01010100101…

(4)

NAND Flash Chip은 해당 주소에 접근하여 데이터를 저장한다.

※ 이때 데이터가 큰 경우 여러 페이지에 걸쳐 저장한다.

다음 주제는 이전에 탐구하고자 했던

BIOS에 대해 탐구해 보겠다.

※ 해당 게시글은 주제를 탐구하면서 주관적인 생각을 정리 한 글입니다.

※ 해당 게시글은 https://www.youtube.com/@BranchEducation SSD 관련 영상을 참고하였습니다.

'[無에서 시작하는 컴퓨터&과학]' 카테고리의 다른 글

| [컴퓨터][35] BIOS에서 운영체제 그리고 고급 프로그래밍 언어의 필요성과 기능 (1) | 2025.03.06 |

|---|---|

| [컴퓨터][34] BIOS (Basic Input/Output System) (1) | 2025.02.26 |

| [컴퓨터][32] 비휘발성 저장 장치 - 2 (자기 테이프, 플로피 디스크, 하드 디스크:HDD) (0) | 2025.02.12 |

| [컴퓨터][31] 비휘발성 저장 장치 - 1 (전자기학 기초 및 자기 와이어 레코딩:magnetic wire recording, 녹음기) (0) | 2025.02.02 |

| [컴퓨터][30] 입출력(I/O) 장치 : 모니터의 원리 (0) | 2024.12.29 |